弊財団では今年度月に1回「「京」を中核とするHPCI活用を見据えたチューニング講習会」を行ってきております。

これまでに産業、学術の分野から広く参加いただき、受講いただいた皆様のアンケートには「より詳しいチューニ ングについて知りたい」、「実習をしてほしい」というご要望がありました。ご要望に沿えるよう、実習を含んだ中級編の講習会を企画致しました。

中級編の講習会は10月より毎月1回開催致します。第1回目の講習会を平成24年10月15日(月)13時から16時の間で計算科学センタービル2階実習室にて開催し、5名の方に参加していただきました。

本講習会は、3部構成となっており、第1部では京やFX10の概要、ノード内メモリ共有のスレッド並列化、ノード内共有メモリとノード間分散メモリを組み合わせたプロセス並列化についての解説を行いました。

第2部ではプログラムチューニングについての解説を行いました。単一プロセスでのチューニング、スレッド並列チューニング、及び京コンピュータに向けたチューニングの方法であるプロセス並列チューニングや並列化効率を高めるための方法についての解説を行いました。

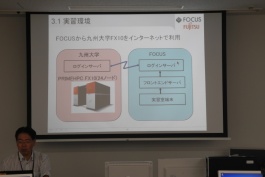

第3部では、九州大学情報基盤研究開発センターのFX10を利用し、「京」と同じアーキテクチャ上でチューニング、コンパイル、実行の実習を行いました。

受講者はコンパイルや計算実行を行うための環境について確認しました。九州大学FX10にログインし、サンプルプログラムや、ジョブ実行用スクリプト、ジョブ管理のためのコマンド(ジョブ投入pjsub、ジョブの状況確認pjstat、ジョブの削除pjdel)などについて確認していただきました。

講師の解説のもと、受講者はサンプラ実行を行いました。サンプラを実行することでコスト分布、性能、キャッシュミスヒットの調査を行うことができます。サブルーチンごとにFLOPS値、MIPS値が表示され、計算性能のよくなサブルーチンを探し出すことができます。また、サブルーチンごとのメモリスループット値からキャッシュのミスヒット(メモリへのアクセス)量を知ることもでき、全体に対する各サブルーチンのコスト分布を知ることもできます。その後、コンパイル時の最適化オプションを変更することで、第2部で学んでいただいたSIMD化の実施、ソフトウェアパイプラインの実施、自動並列化とOpenMPによるスレッド並列を実際に行いました。各々の場合について、コンパイル、プログラムの最適化が行われた箇所の確認(ファイルに出力されます)、サンプラ実行、計算効率の変化の確認していただきました。

講習会終了後ご参加の方々にはアンケートの回答にご協力いただきました。回答結果は本ページ末尾に示します。回答では、事前に4月より行っている基礎編を参加いただいた方からは第1、2部が冗長で第3部の実習が不十分、基礎編に参加いただいていない方からは第1、2部の解説が不十分との要望がありました。これらの要望を受け、プログラム内での時間配分について再検討したいと考えております。

ご参加頂きました皆様、ありがとうございました。 ”「京」を中核とするHPCI活用を見据えたチューニング講習会中級編”は今後も月1回行っていきます。次回は11月12日(月)に開催します。次々回以降はイベントカレンダーを参照いただき、是非今後の講習会にご参加ください。

また、4月より月1回開催している本講習会の基礎編である「「京」を中核とするHPCI活用を見据えたチューニング講習会」も引き続き開催していきます。可能な限りまず基礎編を受講していただいたうえで、実践編にあたる本講習会に参加いただきますようお願い致します。基礎編は次回11月9日(金)に開催致します。以降の日程についてもイベントカレンダーをご覧ください。

講習会についての皆様のご要望やご質問がありましたら request@j-focus.or.jp までお寄せください。

講習会の様子

講習会は3部構成となっております。

1. 基本的な考え方

2. プログラムチューニング

3. 実習

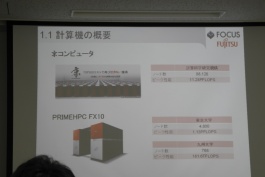

計算機の概要

FX10アーキテクチャの環境は、京コンピュータ(計算科学研究機構)、FX10(九州大学、東京大学)にあります。

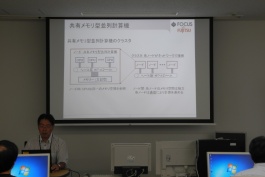

共有メモリ型並列計算機の解説

ノード内にあるCPU間ではメモリを共有しています。各ノードは高速なネットワークでつながっています。

OpenMP指示文による並列化について解説

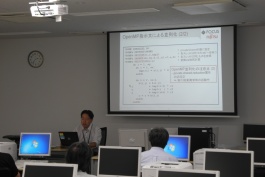

第3部 実習

講師が実習環境について解説。九大FX10にログインして実習を行いました。

受講者も九大FX10へログインして実習を行いました。

コンパイル/実行環境についての解説がありました。

ここではジョブ投入スクリプトの書き方を解説しています。

サンプラの実行

出力ファイルを使って計算効率の解析の実習を行いました。

実習ではSIMD化、ソフトラインパイプライン、スレッド並列について各々の手段を実施する場合、しない場合を比較していただきました。

「京」を中核とするHPCI活用を見据えたチューニング講習会(9月)アンケートおよび回答

プログラム

1) 1.1 計算機の概要 (5分)

2) 1.2 チューニングの考え方 (5分)

3) 2.1 スカラーチューニング (20分)

4) 2.2 スレッド並列チューニング (15分)

5) 2.3 京コンピュータ向けチューニング (30分)

6) 休憩 (10分)

7) 3.1 実習環境 (5分)

8) 3.2 ログイン (5分)

9) 3.3 コンパイル/実行 (25分)

10) 3.4 サンプラ (20分)

11) 休憩 (10分)

12) 3.5 SIMD化 (10分)

13) 3.6 ソフトウェアパイプライニング (10分)

14) 3.7 スレッド並列 (10分)

設問1 1-14)の項目について、内容(長さ)はいかがでしたか?

不十分 十分 過多

-------------------------

1) 4

2) 4

3) 4

4) 4

5) 2 2

6) 4

7) 4

8) 4

9) 4

10) 4

11) 4

12) 1 3

13) 2 2

14) 2 2

設問2 1-14)の項目について、もっとも改善して欲しいものについて要望や

コメントをお願いします。

・ハイブリッドモデルのプログラミング、とあったので、プロセス/スレッド

並列のノウハウ等、濃い話を期待していたので少し残念です。

・問題点のケーススタディ、改善例等があると、より実践的かもと思いました。

・SIMD化されない例を載せてもらうといいと思います。

・SIMD化やpipelineによってどの程度速くなるか例を載せてもらうとわかりやすいと思います。

・12)~14)は早すぎです。時間が短いと思います。

・前半は受講していることを前提にして、すべて実習でもいいのではないでしょうか。

・または、1日のメニューとした方がいいかもしれません。

これまでの講習会開催報告

(基礎編)

【10月12日】「京」を中核とするHPCI活用を見据えたチューニング講習会

【9月14日】「京」を中核とするHPCI活用を見据えたチューニング講習会

【8月10日】「京」を中核とするHPCI活用を見据えたチューニング講習会

【7月13日】「京」を中核とするHPCI活用を見据えたチューニング講習会

【6月8日】「京」を中核とするHPCI活用を見据えたチューニング講習会

【5月11日】「京」を中核とするHPCI活用を見据えたチューニング講習会

【4月13日】「京」を中核とするHPCI活用を見据えたチューニング講習会