2回目となる「京」を中核とするHPCI活用を見据えたチューニング講習会を平成24年5月11日(金)14時から17時まで計算科学センタービル2階実習室にて行いました。

事前登録8名、当日参加7名、産業界及び学術界の両分野から広く参加いただき、「京」を中核とするHPCIへの期待が大きい事を改めて実感しました。

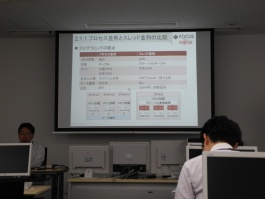

講習会は、HPCIで利用できるスパコンの概要説明から始まり、プロセス並列のみのフラットモデルとプロセス並列とスレッド並列のハイブリッドモデルについての解説や、大規模並列環境である京コンピュータではハイブリッドモデルが推奨されていることが説明されました。

講習会の後半ではSIMD(single Instruction Multiple Data)化、ソフトウェアパイプライニングといった、大規模並列環境におけるプログラムチューニングのノウハウについて解説がなされました。最後には、前回の要望を受けて、ハイブリッドチューニングの事例が紹介され、プロファイルの採集、ソースの変更を経て性能が2倍になったという実例が示されました。

回答いただいたアンケート結果も踏まえまして、次回以降も改良を加えていきたいと思います。

今回、ご参加頂きました皆様、ありがとうございました。

ご都合がつかなかった皆様、次回6月8日(金)、次々回7月13日(金)14時から17時まで計算科学センタービル2階実習室にて行いますのでご参加よろしくお願いします。

プログラム :

1)14:00- 14:05 ( 5分) 開始の挨拶

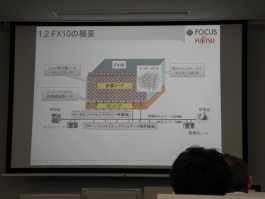

2)14:05- 14:20 (15分) HPCIで利用できるスパコンの概要

3)14:20- 14:35 (15分) ハイブリッド並列プログラミング

4)14:35- 14:45 (10分) プログラム移植

5)14:45- 15:00 (15分) 休憩

6)15:00- 15:45 (45分) プログラムチューニング 前半

7)15:55- 16:40 (45分) プログラムチューニング 後半

8)16:40- 17:00 (20分) Q&A

「京」を中核とするHPCI活用を見据えたチューニング講習会(5月)

アンケートおよび回答

設問1:プログラム1)〜8)の項目について、内容(長さ)はいかがでしたか?

当てはまるものを選んでください。

1)不十分 0 十分 6 過多 0

2)不十分 0 十分 6 過多 0

3)不十分 0 十分 6 過多 0

4)不十分 0 十分 6 過多 0

5)不十分 0 十分 4 過多 2

6)不十分 0 十分 6 過多 0

7)不十分 1 十分 5 過多 0

8)不十分 0 十分 6 過多 0

設問2:1)〜8)の項目について、もっとも改善して欲しいものについて要望やコメントをお願いします。

・京へのJobの流し方などの実際の運用についてもう少し知りたかったです。

・ファイルシステムの説明等があればいいと思います。

・配布資料が白黒でみずらい。

・電子ファイル(メール添付)で配布していただけませんか?

・4.5.2 SIMD化、4.5.3 ソフトウェアパイプライニングについて、

SIMD化、パイプライニング前後のコードと、計算コストの改善例等具体的例がうかがえれば良かったと思います。

・計算コスト改善の為の自分の認識を再確認させていただく機会をもらえて良かったと思います。